# Cheatography

## CS 232 Computer Organization Final Cheat Sheet by louielegrand via cheatography.com/27914/cs/8200/

| Terminology                    |                         | Basic Identities                                |                                       |                         | Decoder                                                                                    | Cache                                                                     |

|--------------------------------|-------------------------|-------------------------------------------------|---------------------------------------|-------------------------|--------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|

| Tera                           | 10 <sup>12</sup>        | Name                                            | AND form                              | OR form                 | n data inputs                                                                              | Component that stores                                                     |

| Giga                           | 10 <sup>9</sup>         | (Law)                                           |                                       |                         | D, 2 <sup>n</sup> data outputs                                                             | data to speed up future                                                   |

| Mega                           | 106                     | Identity                                        | 1A = A                                | 0+A = A                 |                                                                                            | search requests. Cache<br>hit - data can be found                         |

| Kilo                           | 10 <sup>3</sup>         | Null                                            | 0A = 0                                | 1+A = 1                 | $\overline{R}$ $\overline{D_{0}}$ $3$ -to-8 decoder                                        | vs Cache miss - data                                                      |

| 1 GHz                          | 1x10 <sup>9</sup> Hz    | Idempotent                                      | AA = A                                | A+A = A                 |                                                                                            | cannot be found. Hit rate                                                 |

| 1 TB                           | 1x10 <sup>12</sup> Byte | Inverse                                         | AA = 0                                | A+A = 1                 |                                                                                            | <ul> <li>% of accesses resulting<br/>in cache hits. Relatively</li> </ul> |

| 1 Byte                         | 8 Bits                  | Commutativ                                      | AB = BA                               | A+B = B+A               |                                                                                            | small due to cost.                                                        |

| Т Буїе                         | o Dits                  | е                                               |                                       |                         |                                                                                            | Locality of reference -                                                   |

| Conversi                       | ions                    | Associative                                     | (AB)C =                               | (A+B)+C =               | Other Sequential Circuits                                                                  | Temporal locality: reuse                                                  |

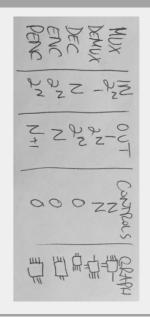

| Binary                         | Hex Dec                 | <b>D</b>                                        | A(BC)                                 | A+(B+C)                 | Multiplexer                                                                                | of specific data, and/or resources, within a                              |

| 1111                           | 0F 15                   | Distributive                                    | A+BC =<br>(A+B)(A+C)                  | A(B+C) =<br>AB+AC       | Demultiplexer                                                                              | relatively small time                                                     |

|                                |                         | Absorption                                      | A(A+B) = A                            | A + AB = A              | Decoder                                                                                    | duration. Spatial locality:                                               |

| Hex                            |                         | DeMorgan's                                      | AB = A+B                              | A+B = AB                | Encoder                                                                                    | use of data elements<br>within relatively close                           |

| In Hex, each digit             |                         | Donnorganio                                     |                                       |                         | Priority Encoder                                                                           | storage locations.                                                        |

| represents 4 binary bits (i.e. |                         | Boolean Concepts                                |                                       |                         |                                                                                            | Tradeoff: Larger caches                                                   |

| 1111 1111 is FF)               |                         | Addition Subtraction                            |                                       |                         | Byte Ordering                                                                              | have better hit rates but                                                 |

|                                |                         | 1+1 = 10 0-1 = 1 (borrow method)                |                                       | w method)               |                                                                                            | longer latency. Small<br>fast caches backed up                            |

| 2's Complement                 |                         |                                                 |                                       |                         | to right or right to left. Big-endian: Most                                                | by larger, slower caches.                                                 |

| 0111                           | 7                       | All other operations straightforward.           |                                       | orward.                 | significant byte (byte containing most                                                     | Multi-level caches:                                                       |

| 1000                           | -8                      |                                                 |                                       |                         | significant bit) is stored first and following bytes are stored in decreasing significance | check fastest L1 cache<br>first; if it hits, proceeds at                  |

| 1111                           | Boolean Concepts II     |                                                 | order. Little-endian is the opposite. | HS. If L1 misses, L2 is |                                                                                            |                                                                           |

| Logic Gates                    |                         | Carry out: Carry out of leftmost bit            |                                       |                         |                                                                                            | checked, and so on,                                                       |

|                                |                         | Overflow: Result too large or small to fit into |                                       |                         | Memory Hierarchy                                                                           | before accessing                                                          |

| AND                            | AB                      | bits                                            |                                       |                         | In order of increasing access time, storage                                                | external memory                                                           |

| OR                             | A+B                     |                                                 |                                       |                         | capacity, and bits you get per dollar spent:                                               |                                                                           |

| NOT                            | A                       | S-R Latch                                       |                                       |                         | Registers; Cache; Main Memory; Magnetic<br>or solid state disk; Tape or Optical Disk.      |                                                                           |

| NAND                           | AB                      | R                                               | + Q SR                                | o ō                     |                                                                                            |                                                                           |

| NOR                            | A+B                     |                                                 | 0 0 1                                 | latch latch             |                                                                                            |                                                                           |

| XOR                            | A B                     |                                                 | 1 0                                   | 1 0                     |                                                                                            |                                                                           |

| XOR Truth Table                |                         |                                                 |                                       | 0 0                     |                                                                                            |                                                                           |

|                                |                         |                                                 |                                       |                         |                                                                                            |                                                                           |

| A B                            | A XOR B                 |                                                 |                                       |                         |                                                                                            |                                                                           |

| 0 0                            | 0                       |                                                 |                                       |                         |                                                                                            |                                                                           |

| 0 1                            | 1                       |                                                 |                                       |                         |                                                                                            |                                                                           |

| 1 0                            | 1                       |                                                 |                                       |                         |                                                                                            |                                                                           |

1

0

1

### By louielegrand

cheatography.com/louielegrand/

Not published yet. Last updated 14th May, 2016. Page 1 of 2.

Sponsored by Readability-Score.com Measure your website readability! https://readability-score.com

# Cheatography

## CS 232 Computer Organization Final Cheat Sheet by louielegrand via cheatography.com/27914/cs/8200/

| Cache Mapping                                                                       |                                           |                                     |  |  |  |  |  |

|-------------------------------------------------------------------------------------|-------------------------------------------|-------------------------------------|--|--|--|--|--|

| Cache<br>type                                                                       | Hit Ratio                                 | Search<br>speed                     |  |  |  |  |  |

| Direct<br>Mapped                                                                    | Good                                      | Best                                |  |  |  |  |  |

| N-Way<br>Set<br>Associat<br>ive                                                     | Very good,<br>better as<br>N<br>increases | Good,<br>worse as<br>N<br>increases |  |  |  |  |  |

| Fully<br>associat<br>ive                                                            | Best                                      | Moderate                            |  |  |  |  |  |

| Replacement Algorithms                                                              |                                           |                                     |  |  |  |  |  |

| Optimize management of cache -<br>chooses which items to discard in<br>a full cache |                                           |                                     |  |  |  |  |  |

| Each is a tradeoff between latency and hit ratio                                    |                                           |                                     |  |  |  |  |  |

| Common: LRU, MRU, RR, 2-way set, Direct-mapped                                      |                                           |                                     |  |  |  |  |  |

| Write Policy                                                                        |                                           |                                     |  |  |  |  |  |

#### Write-Write-back through Write initially only to Write is done cache; write to main synchron memory postponed ously until cache blocks both to containing data are cache about to be modified/replaced and main mem ADV: ADV: Faster, uses Simpler less memory bandwidth and more reliable, mem is always up-todate

| Write Policy (cont) |           |

|---------------------|-----------|

| DISADV: Write is    | DISADV:   |

| slower, every write | More      |

| requires main       | complex,  |

| memory access,      | must      |

| uses more memory    | track     |

| bandwidth           | "dirty"   |

|                     | locations |

|                     |           |

#### Mean access time

mean access time = c + (1-h)mc - cache access time h - hit ratio

m - main memory access time

### Data Dependencies

(RAW)

WAR

WAW

True data Occurs when an dependency instruction depends on result of previous instruction Occurs when an instruction requires a value that is later updated Occurs when the ordering of instructions will affect the final output value of a variable

| RISC                                                                                  |  |  |  |  |  |

|---------------------------------------------------------------------------------------|--|--|--|--|--|

| Emphasis on software                                                                  |  |  |  |  |  |

| Single-clock,<br>reduced<br>instruction only                                          |  |  |  |  |  |

| Register-to-reg<br>ister: "LOAD"<br>and "STORE"<br>are<br>independent<br>instructions |  |  |  |  |  |

| Low cycles per<br>second, large<br>code sizes                                         |  |  |  |  |  |

| LOAD LOAD<br>PROD STORE                                                               |  |  |  |  |  |

| Performance equation                                                                  |  |  |  |  |  |

| time/program = time/cycle x<br>cycles/instruction x<br>instructions/program           |  |  |  |  |  |

| CISC minimzes instructions per<br>program at cost of cycles per<br>instruction        |  |  |  |  |  |

|                                                                                       |  |  |  |  |  |

RISC reduces cycles per instruction at cost of number of instructions per program

#### State Machines

Moore Machines: output is a function of the state

Mealy Machines: output is a function of the state and the input

Portion of a machine language that specifies the operation to be performed

### Addressing modes Immediate Direct Indirect Reg Direct Reg Indirect Reg Base-Ind Reg Base-Scaled Ind Basic ISA Classes Load/Store Stack Gen Accumu lator Purp Reg 1 or 1+x 0 2 or 3 3 address address

address address

### Speedup Calculation

Speedup =  $(NT^1)/[K+(N-1)]T$

Where N is # of instructions, T1 is time for stage 1 CPU to complete instruction

K is # of stages for multistage and T is time for step + latch

#### By louielegrand

cheatography.com/louielegrand/

Not published yet. Last updated 14th May, 2016. Page 2 of 2.

Sponsored by Readability-Score.com Measure your website readability!

https://readability-score.com