### STY 2013 Final Cheat Sheet

by [deleted] via cheatography.com/5328/cs/965/

| assembly: registers and flags |                                                          |  |  |  |  |  |  |

|-------------------------------|----------------------------------------------------------|--|--|--|--|--|--|

| %eax   %ecx                   | Temporary data,                                          |  |  |  |  |  |  |

| %edx   %ebx                   | General purpose                                          |  |  |  |  |  |  |

| %esi   %edx                   | registers                                                |  |  |  |  |  |  |

| %esp   %ebp                   | Current: stack top                                       |  |  |  |  |  |  |

|                               | stack frame                                              |  |  |  |  |  |  |

| %eip                          | Instruction pointer                                      |  |  |  |  |  |  |

| CF   ZF   SF   OF             | Carry flag   Zero flag<br>  Sign flag   Overflow<br>flag |  |  |  |  |  |  |

| Note: | flans | are | not | Set | hν | lea. | instruction. |

|-------|-------|-----|-----|-----|----|------|--------------|

|       |       |     |     |     |    |      |              |

| assembly: jumps and shifts           |                                                                |  |  |  |  |

|--------------------------------------|----------------------------------------------------------------|--|--|--|--|

| sal   sar                            | arithmetic shift left   right                                  |  |  |  |  |

| shl   shr                            | logical shift left   right                                     |  |  |  |  |

| jz   jnz                             | jump if == 0,"zero"   != 0,"not zero"                          |  |  |  |  |

| je   jne   jg<br>  jge   jl  <br>jle | jump if ==   !=   >   >=   <   <=                              |  |  |  |  |

| js                                   | jump and store                                                 |  |  |  |  |

| jmp   jmp<br>*reg                    | unconditional relative jump  absolute jump, reg is a registry. |  |  |  |  |

| ja   jb<br>(unsigned)                | jump above   below                                             |  |  |  |  |

| assembly: compares and flags |                  |  |  |  |  |

|------------------------------|------------------|--|--|--|--|

| cmp b, a                     | a - b            |  |  |  |  |

| test b, a                    | a & b            |  |  |  |  |

| zf "zero flag"               | set when a&b== 0 |  |  |  |  |

| sf "signed flag"             | set when a&b < 0 |  |  |  |  |

| assembly: getting setting                               |                                                              |  |  |  |  |  |

|---------------------------------------------------------|--------------------------------------------------------------|--|--|--|--|--|

| lea a, b                                                | load effective address a into b                              |  |  |  |  |  |

| mov a, b                                                | move contents of a into b                                    |  |  |  |  |  |

| cmov (z,nz,e,n-<br>e,g,ge,l,le,ng,-<br>nge,nl,nle,a,b,) | compare and move if condition is met.                        |  |  |  |  |  |

| movl %edx, %eax                                         | eax = edx, eax bendir<br>á edx                               |  |  |  |  |  |

| movl (%edx),<br>%eax                                    | eax = *edx, eax<br>verður bendir á<br>innihald edx           |  |  |  |  |  |

| movl %edx,<br>(%eax)                                    | *eax = edx, eax<br>bendir á bendinn að<br>innihaldi edx      |  |  |  |  |  |

| movl (%edx),<br>(%eax)                                  | eax = edx, yfirskrifar<br>innihald eax með<br>innihaldi edx. |  |  |  |  |  |

| Arro | / shizz | zmit  |

|------|---------|-------|

| Αща  |         | 41111 |

|      |         |       |

address(mn[i][j]) = 0+i\*N+4jaddress(nm[i][j]) = 0+i\*M+4j

Given the arrays:

int mn[M][N]; and int nm[N][M];

#### Reading a disk sector(sequence)

- 1: CPU initiates disk read, writes cmd, lbn and desk to a DC port(address)

- 2: DC reads sector and performs a DMA transfer into main memory

- 3: DC notifies CPU with *interrupt* signal when DMA transfer completes

DC: Disk controller

DMA: direct memory access

cmd: command

Ibn: logical block number

dest: destination

Published 22nd April, 2013. Last updated 13th May, 2016. Page 1 of 2.

| Memory system parameters |                                               |  |  |  |  |

|--------------------------|-----------------------------------------------|--|--|--|--|

| N=2 <sup>n</sup>         | Number of addresses in virtual address space  |  |  |  |  |

| M=2 <sup>m</sup>         | Number of addresses in physical address space |  |  |  |  |

| P=2 <sup>p</sup>         | Page size(bytes)                              |  |  |  |  |

|                          |                                               |  |  |  |  |

| Components of PA(physical address)  |     |  |  |  |  |

|-------------------------------------|-----|--|--|--|--|

| PPO Physical page offset(same as VI | 20) |  |  |  |  |

| PPN Physical page number.           |     |  |  |  |  |

| CO Byte offset within cache line    |     |  |  |  |  |

| CI Cache index                      |     |  |  |  |  |

| CT Cache tag                        |     |  |  |  |  |

| Components of VA(Virtual Address) |                     |  |  |  |

|-----------------------------------|---------------------|--|--|--|

| TLBI                              | TLB index           |  |  |  |

| TLBT                              | TLB tag             |  |  |  |

| VPO                               | Virtual page offset |  |  |  |

| VPN                               | Virtual page number |  |  |  |

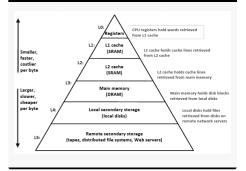

#### Locality

#### Temporal locality:

> Recently referenced items are likely to be referenced again in the near future.

#### Spatial locality:

> Items with nearby addresses tend to be referenced close together in time.

#### **Memory Hierarchy**

C

By [deleted] cheatography.com/deleted-5328/ Sponsored by **Readable.com**Measure your website readability!

https://readable.com

## STY 2013 Final Cheat Sheet

by [deleted] via cheatography.com/5328/cs/965/

#

#### Simple Memory System Cache

| <ul> <li>16 lines, 4-byte block size</li> <li>Physically addressed</li> </ul> |     |       |    |      |     |     |     |      |       |    |    |    |    |

|-------------------------------------------------------------------------------|-----|-------|----|------|-----|-----|-----|------|-------|----|----|----|----|

| ■ Direct mapped                                                               |     |       |    |      |     |     |     |      |       |    |    |    |    |

|                                                                               |     | •     |    |      | т — | -   | -   | — сі |       | co | →  |    |    |

|                                                                               |     | _ 11  | 10 | 9    | 8   | 7 6 | 5   | 4    | 3 2   | 1  | 0  |    |    |

|                                                                               |     |       |    |      |     |     |     |      |       |    |    |    |    |

|                                                                               |     | •     |    | — PP | N - |     | -   |      | PPO - |    | -  |    |    |

| Idx                                                                           | Tag | Valid | B0 | BI   | B2  | B3  | ldx | Tag  | Valid | В0 | B1 | B2 | В  |

| 0                                                                             | 19  | 1     | 99 | 11   | 23  | 11  | 8   | 24   | 1     | ЗА | 00 | 51 | 89 |

| 1                                                                             | 15  | 0     | -  | -    | -   | -   | 9   | 2D   | 0     | -  | -  | -  | _  |

| 2                                                                             | 18  | 1     | 00 | 02   | 04  | 08  | A   | 2D   | 1     | 93 | 15 | DA | 38 |

| 3                                                                             | 36  | 0     | -  | -    | -   | -   | В   | 0B   | 0     | -  | -  | -  | -  |

| 4                                                                             | 32  | 1     | 43 | 6D   | 8F  | 09  | С   | 12   | 0     | -  | -  | -  | -  |

| 5                                                                             | 0D  | 1     | 36 | 72   | FO  | 1D  | D   | 16   | 1     | 04 | 96 | 34 | 15 |

| 6                                                                             | 31  | 0     | -  | -    | -   | -   | E   | 13   | 1     | 83 | 77 | 1B | D: |

|                                                                               |     | 1     | 11 | C2   | DF  | 03  | F   | 14   | 0     | _  | _  |    |    |

#### Cache

TLB holds recently used PTE's, located on the cpu chip.

PTE Page table entry, physical address of data in cache/memory

| Sigr | nals    |                          |                             |

|------|---------|--------------------------|-----------------------------|

| ID   | Name    | Default<br>Action        | Event                       |

| 2    | SIGINT  | Terminate                | Interupt,ctrl-<br>c         |

| 9    | SIGKILL | Terminate                | Kill (unavo-<br>idable)     |

| 11   | SIGSEGV | Termin-<br>ate-<br>&Dump | Segfault                    |

| 14   | SIGALRM | Terminate                | Timer signal                |

| 15   | SIGTERM | Terminate                | Kill nicely-<br>(catchable) |

| 17   | SIGCHLD | Ignore                   | Child stoppd or killd       |

By [deleted] cheatography.com/deleted-5328/ Published 22nd April, 2013. Last updated 13th May, 2016. Page 2 of 2. Sponsored by **Readable.com**Measure your website readability!

https://readable.com